### Lab 8: FPGA/DAC

UC Davis Physics 116B Rev 3/7/2019.2

# Introduction

In this lab, you will use the skills you've acquired with VHDL and the Spartan 3E development board to experiment with the on-board digital to analog converter (DAC).

### **Pre-lab Exercises**

For this lab, we will use the quad DAC on the Spartan 3E development board. This DAC has four 12-bit DACs, two of which have  $V_{ref}$ =3.3V and two of which have  $V_{ref}$ =2.5V. The output voltage of each DAC will be

$$V_{out} = \frac{D}{2^{12}} V_{ref}$$

$$= \frac{D}{4096} V_{ref}$$

For each reference voltage, calculate the voltage change associated with the least significant bit (LSB), as well as the voltage change associated with each of the four most significant bits [11-8].

# **Files Provided for this Lab**

You will be provided with the "DAC\_SET.vhd" module to convert parallel words into the serial data to program the on-board DAC, which we discussed in detail in class. You will also be provided with the "pins.ucf" file to constrain the pin positions<sup>1</sup>. These files are located in the Files/Labs/Lab\_8 Files area of the course Canvas page, and they will also be available on USB stick.

Listings of these two files are included in the Appendix of this document. Be sure you understand them.

# Spartan 3E On Board Quad DAC

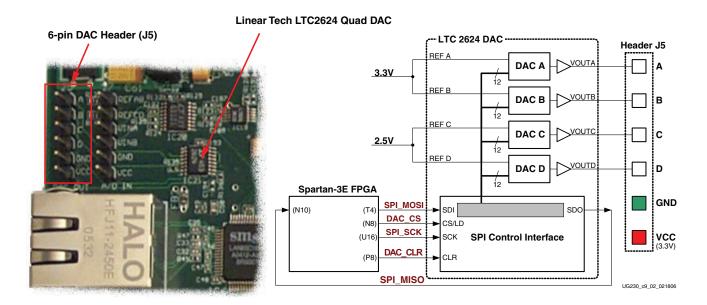

Figure 1 shows the location of the LT2624 quad DAC, its associated output header, and a schematic representation of its operation. The chip contains 4 12-bit DACs, two of which have  $V_{ref}$ =3.3V

<sup>&</sup>lt;sup>1</sup>There are lots of pins to connect, and you've already demonstrated you know how to do this.

and two of which have  $V_{ref}$ =2.5V. Each DAC may be set individually to a different value of D, or all DACs may be setting simultaneously to the same value of D.

The DAC chip is configured by means of an active low chip select (DAC<sub>-</sub> CS), a serial data line (SPI<sub>-</sub> MOSI), and a serial data clock (SPI<sub>-</sub>SCK). In addition, an active low reset (DAC<sub>-</sub>CLR) must be kept high for normal operation! The capability exists to read back the configuration data through the SPI<sub>-</sub> MISO pin, but we will not do this.

Figure 1: Location of on-board DAC and output header on Spartan 3E Starter Board, including schematic representation their operation.

You are being provided with the "DAC\_SET.vhd" module to perform the actual configuration of the DAC, but it's important to understand its operation, which we discussed in class.

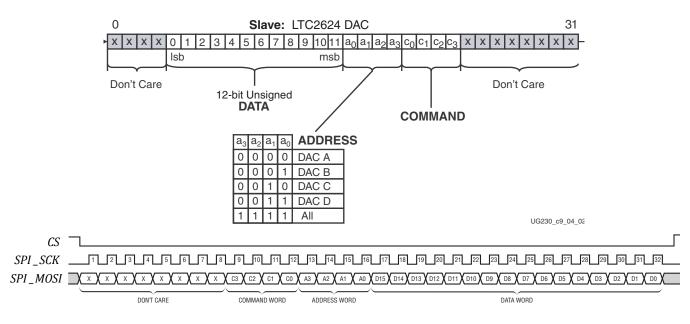

| bits  | Use     | Comment                                                 |

|-------|---------|---------------------------------------------------------|

| 3-0   | _       | Don't care                                              |

| 15-4  | DAC     | 12-bit DAC setting                                      |

| 19-16 | ADDRESS | "0000" $\rightarrow$ set DAC A                          |

|       |         | " $0001$ " $\rightarrow$ set DAC B                      |

|       |         | " $0010$ " $\rightarrow$ set DAC C                      |

|       |         | " $0011$ " $\rightarrow$ set DAC D                      |

|       |         | "1111" $\rightarrow$ set ALL                            |

| 23-20 | COMMAND | We will use COMMAND="0011", which will promptly         |

|       |         | set the DAC and enable it at the end of the write cycle |

| 31-24 | _       | Don't care                                              |

Figure 2: DAC configuration encoding and time line.

The DAC is configured by means of a 32-bit configuration word, defined in Table 1. Figure 2 illustrates this packed word, as well as the programming sequence. DAC\_CS goes low, and the 32 bits of the configuration word are asserted onto SPI\_ MOSI, starting with the MSB. While each bit is valid, a rising edge on SPI\_SCK clocks it into the DAC chip. After 32-bits have been loaded into the DAC, DAC\_CS goes high again. We will always use COMMAND="0011", which will cause the selected DAC to immediately go to the set value at this point.

# **VHDL Code**

Start a new project and define a new VHDL module with the following inputs and outputs:

```

entity LAB8 is

Port (CLK : in

STD_LOGIC;

-- On board 50 MHz clock

STD_LOGIC_VECTOR (3 downto 0); -- On Board slide switches

SW : in

LED : out STD_LOGIC_VECTOR (7 downto 0); -- On Board LEDs

DAC_CS : out STD_LOGIC;

-- Chip select to DAC

SPI_MOSI : out

STD_LOGIC;

-- Serial Data bit to DAC

-- Serial Clock to DAC

SPI_SCK : out STD_LOGIC;

DAC_CLR : out STD_LOGIC;

-- DAC clear. MUST BE SET TO '1'!

J1 : out STD_LOGIC_VECTOR (3 downto 0)); -- General purpose diagnostic pins

end LAB8;

```

You have been provided with the "DAC\_SET.vhd" module, but you must prototype it with the

following component specification before the "begin" line of the architecture block<sup>2</sup>:

```

component DAC_SET is

Port ( CLK : in STD_LOGIC;

DAC : in STD_LOGIC_VECTOR (11 downto 0);

ADDRESS: in STD_LOGIC_VECTOR (3 downto 0);

COMMAND : in STD_LOGIC_VECTOR (3 downto 0);

SET : in STD_LOGIC;

BUSY : out STD_LOGIC;

DAC_CS : out STD_LOGIC;

MOSI : out STD_LOGIC;

SCK : out STD_LOGIC;

end component;

```

In this area, you must also define the DAC, ADDRESS, COMMAND, SET, and BUSY signals, with the appropriate sizes. The remaining signals from DAC\_SET *could* be tied directly to corresponding pins of the main module, but as we'll discuss below, we want to tie them to two different outputs, so you should also create the inermediate STD\_LOGIC signals CS,MOSI, and SCK.

In the concurrent section of the code (after "begin"), you can instantiate the DAC\_SET module with

D: DAC\_SET port map(CLK,DAC,ADDRESS,COMMAND,SET,BUSY,CS,MOSI,SCK);

You'll then need to tie CS, MOSI, and SCK to DAC\_CS, SPI\_MOSI, and SPI\_SCK, respecively.

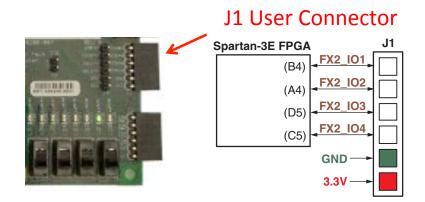

Because the pins on the DAC chip are very small, it's difficult to look directly at the configuration signals with an oscilloscope, so in addition to the connections above we'll tie the following four signals to the four elements of the J1 vector as well: SET, CS, MOSI, and SCK. This will allow us to monitor them at the J1 connector on the board, shown in Figure 3.

Now make the following connections:

- Set DAC\_CLR to '1' to prevent the DAC from going into a permanently reset state<sup>3</sup>.

- Set COMMAND to "0011". This will cause the DAC output to go to the set value immediately when DAC\_CS goes high. Other values would allow it to be, for example, set in one cycle, and then turned on later.

- Tie LED[3:0] to the ADDRESS[3:0].

- The LED[7:4] to DAC[11:8] (four most significant bits) of DAC setting.

<sup>&</sup>lt;sup>2</sup>It might save time to copy the port() part of this directly from the "DAC\_SET.vhd" file.

<sup>&</sup>lt;sup>3</sup>The author learned this the hard way.

Figure 3: Location, pinouts, and FPGA mapping of the J1 general purpose header.

Once you have created your project and written the outline of your code, you should copy the "DAC\_SET.vhd" and "pins.ucf" files to the project directory and "Add Source..." them to your main VHDL file.

We will now set the DAC in two different ways. In the first part, we will set all the DACs to a constant value by using the switches to set the highest order bits. In the second part, we will generate a sawtooth wave by incrementing the DAC setting by one each time we set the DAC.

As an optional third part, you may modify the code to generate a triangle wave instead of a sawtooth wave.

### Setting the DACs to a Constant Value

For this section, tie DAC[7:0] to "00000000", and DAC[11:8] to the four slider switches. This effectively turns our 12-bit DACs into 4-bit DACs.

Next, create a process which will test on the rising edge of CLK, and inside that IF block, test on the BUSY and SET signals. If BUSY='0' and SET='0', assert the SET bit. In other words, set the DAC as often as you can.

Compile the code, generate the bit file, and program it to the FPGA. Verify that the four lower LEDs are all ON (ADDRESS="1111"), and that the slide switches are reflected in the LED[7:4] (DAC[11:8]).

Now use the scope to look at the configuration signals on the J1 header (see Figure 3). You can ground the probes to the "gnd" pins provided on the board. First trigger on the DAC\_CS pin going high (i.e. the end of the configuration cycle), and also look at the SET pin. If you wrote your code correctly, you should see the DAC\_CS pin going high for two 50 MHz clock cycles, with the SET pin going high for the second. Verify that this is the case, and for your writeup, draw a timeline of the (expected) CLK, SET, BUSY, and DAC\_CS signals to explain why this is so. Your writeup should also include an image of the scope traces.

Now trigger on the DAC\_CS pin going low, and set the time scale so that you can see its entire

length. The configuration should take 1 clock cycle to set up, followed by 32 serial bits, each of which takes 2 clock cycles, for a total of 65 50 MHz clock cycles. Verify that this is the length of time the DAC\_CS signal remains low.

Using a second scope probe, look at the SPI\_MOSI data pin. Because COMMAND="0011" and ADDRESS="1111", you should see six sequential bits always high, while manipulating the switches should change the state of the four bits immediately after those, and all other bits should be 0. Start with all switches set to '0', then turn them on one at a time and observe whether the SPI\_MOSI bit behaves as expected. Include pictures of scope traces with at least two different switches set.

If all of this looks correct, use the DVM to measure the voltage between ground and the DAC output pins at header J5 (see Figure 1). Because ADDRESS="1111", changing any of the switch settings should change the output of all four DACs. Verify that this is so.

Now, looking just at the output of DAC A ( $V_{ref} = 3.3V$ ), measure the amount the voltage changes when you change the state of each of the four switches, and confirm that the change matches your predictions from the pre-lab exercises. Your lab write-up should include your predicted and observed values.

#### **Generating a Sawtooth Wave**

In this section, we'll replace the constant DAC setting with a setting that ramps through all  $2^{12}$  possible settings, and then loops around, generating a sawtooth wave.

First, make the following changes in the concurrent section of your code:

- Eliminate the assignment of the lower 8 DAC bits to "000000".

- Eliminate the connection of the higher 4 DAC bits to the switches.

- Eliminate the assignment of ADDRESS to "1111" and instead tie the ADDRESS bits to the switches.

In the process section, create a new variable (between "process" and "begin") called "dac\_value" that is an integer with a range of 0 to 4095, which is initialized to 0. Tie this to the DAC bits with

DAC <= std\_logic\_vector(to\_unsigned(dac\_value,12));</pre>

and increment it each time you assert the SET signal. Compile the code, generate the bit file and program it to the FPGA.

Turn all switches ON and verify that all four DACs are producing sawtooth waves. Verify that the maximum values are what you expect for the AB and CD pairs, based on their respective values for  $V_{ref}$ .

Next, make just one DAC at a time ramp but setting the switches to the values indicated in Table 1, and verify that none of the others change when you do this.

In the last section, you (hopefully) showed that each SET cycle took 65+2=67 cycles of the 50 MHz clock. Based on this, calculate the expected period of the sawtooth wave; i.e. the time it takes to go through all 4096 values. Verify this matches the period you observe on the scope.

For your lab writeup, include your code and the scope trace of the sawtooth wave.

### **OPTIONAL:** Triangle Wave

If you have time, modify your code to produce a triangle wave instead of a sawtooth wave, by counting up through all values, then counting down through all values.

Appendix: Pin-outs and DAC\_SET.vhd Routine

```

1 # These the pinouts needed for the FPGA/DAC Lab in

2 # P116B at UC Davis

3

# 20190226 - E. Prebys

4 # Slide switches, used for configuration

5 NET "SW<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ;

6 NET "SW<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ;

7 NET "SW<2>" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ;

8 NET "SW<3>" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP ;

9 # For the next part, ClK is tied to the onboard 50 MHz

10 #onboard 50 MHz

11 NET "CLK" LOC = "C9";

12

13 #LED Outputs

14 NET "LED<0>" LOC = "F12";

15 NET "LED<1>" LOC = "E12";

16 NET "LED<2>" LOC = "E11";

17 NET "LED<3>" LOC = "F11";

18 NET "LED<4>" LOC = "C11";

19 NET "LED<5>" LOC = "D11";

20 NET "LED<6>" LOC = "E9";

21 NET "LED<7>" LOC = "F9";

22

23 #General purpose IO, to monitor the DAC signals

24 NET "J1<0>" LOC = "B4"; # | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 6 ;

25 NET "J1<1>" LOC = "A4"; # | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 6 ;

26 NET "J1<2>" LOC = "D5";# | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 6 ;

27 NET "J1<3>" LOC = "C5"; # | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 6 ;

28

29 #serial control for DAC, AMP, and ADC, uncomment as needed

30 #common

31 # serial clock

32 NET "SPI SCK" LOC = "U16" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

# data input to chips (output from FPGA)

33

34 NET "SPI MOSI" LOC = "T4" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 6 ;

35 # data output from chips (input to FPGA)

36 #NET "SPI MISO" LOC = "N10" | IOSTANDARD = LVCMOS33 ;

37

38 # select bits

39 # Amplifier

40 #NET "AMP CS" LOC = "N7" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 6 ;

41 # ADC

#NET "AD CONV" LOC = "P11" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 6 ;

42

43 # DAC

44 NET "DAC CS" LOC = "N8" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

45 NET "DAC CLR" LOC = "P8" | IOSTANDARD = LVCMOS33 | SLEW = SLOW | DRIVE = 8 ;

```

```

1

-- Company: UC Davis

2

-- Engineer: Eric Prebys

3

4

___

-- Create Date:

10:55:47 02/06/2019

5

DAC_SET

-- Design Name:

6

-- Module Name: DAC_SET - Behavioral

-- Project Name: UC Davis P116B FPGA Lab 3

7

8

-- Target Devices: xc3s500e-4fg320

9

-- Tool versions: ISE 14.7

10

-- Description:

11

-- Will set the Linear Tech LTC2624 Quad DAC 12-bit DAC on the

12

Spartan 3E starter board. It will take 65 clock cycles, following

13

___

the synchronous assertion of the SET pin.

14

___

___

15

IMPORTANT NOTE: In addition to the pins driven by this component,

16

___

the DAC_CLR pin (pin P8 on Xilinx Chip) must be driven HI to

17

___

prevent the DAC from remaining in a RESET state!

18

___

19

___

-- Inputs:

20

___

CLK

– 50MHz onboard clock

21

- 12-bit DAC setting

DAC

22

___

ADDRESS

- 4-bit address word (0-3 \rightarrow DAC#, 15 \rightarrow ALL)

23

___

- 4-bit command word (usually "0011")

COMMAND

24

___

- begin set process

25

SET

___

-- Ouputs:

26

BUSY – setting in progress (active HI)

27

___

(tie the following directly to the DAC)

28

___

DAC CS – amp chip select (active LOW)

29

___

MOSI – serial data bits

30

___

- serial clock, clocked at 1/2 of CLK speed. Ambiently LOW, so

SCK

31

___

it can be ORed with other SCK drivers

32

___

33

-- Dependencies: NONE

34

___

-- Revision:

35

-- Revision 0.01 - File Created 2/06/2019 - E.Prebys

36

37

Based on AMP SET

___

2/07/2019 - E.Prebys

38

1.00

___

Working version. Cleaned up and commented.

39

___

-- Additional Comments:

40

41

___

42

43 library IEEE;

44 USE IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

45

```

```

entity DAC SET is

46

Port ( CLK : in STD_LOGIC;

47

DAC : in STD_LOGIC_VECTOR (11 downto 0);

48

ADDRESS: in STD_LOGIC_VECTOR (3 downto 0);

49

COMMAND : in STD LOGIC VECTOR (3 downto 0);

50

SET : in STD_LOGIC;

51

BUSY : out STD LOGIC;

52

DAC CS : out STD LOGIC;

53

MOSI : out STD_LOGIC;

54

SCK : out STD_LOGIC);

55

end DAC_SET;

56

57

architecture Behavioral of DAC SET is

58

59

-- This is a 32 bit word that encodes the DAC, ADDRESS, and COMMAND words

60

signal SETWORD: STD LOGIC VECTOR (31 downto 0);

61

62

63 begin

64

-- Pack the individual words into one 32 bit setword (see manual)

65

66 SETWORD(3 downto 0) <= "0000"; -- Don't care

67 SETWORD(15 downto 4) <= DAC;

-- 12-bit DAC setting

68

SETWORD(19 downto 16) <= ADDRESS;</td>

-- 4-bit ADDRESS (0-3=DAC#, 15=ALL)

69

SETWORD(23 downto 20) <= COMMAND;</td>

-- 4-bit COMMAND (usually "0011")

70 SETWORD(31 downto 24) <= "000000000"; --- Don't care

71

72 process(CLK,SET)

-- This state machine is ambiently in the IDLE state, with

73

74 --- DAC CS HI, BUSY LOW, and SCK LOW

75

___

-- In response to a SET, it will assert a BUSY HI and DAC CS LOW

76

77 -- It will then go through 32 2-CLK cycles of LOW, HI,

-- referring to the SCK state. the appropriate DAC

78

-- bit will be asserted on MOSI at state LOW and held through

79

-- HI, starting with the MSB. After 32 bits, it will return to IDLE.

80

81

___

type state_type is (IDLE,LOW,HI);

82

variable state: state type;

83

84

variable bit index: integer range 0 to 31 := 31;

85

begin

86

if rising_edge(CLK) then

87

case state is

88

when IDLE =>

—— Ambiently keep SCK and BUSY low, DAC_C

89

SCK <= '0';

90

```

```

91

BUSY <= '0';

DAC_CS <= '1';

92

if SET = '1' then

93

BUSY <= '1';

94

DAC CS <= '0';

95

bit index := 31;

-- MSB first

96

state := LOW;

97

end if;

98

when LOW =>

-- SCK low

99

SCK <= '0';

100

state := HI;

101

MOSI <= SETWORD(bit index);</pre>

102

when HI =>

-- SCK edge clocks in data

103

SCK <= '1';

104

if bit_index > 0 then

105

state := LOW;

106

bit_index := bit_index -1;

107

else

108

state := IDLE;

109

end if;

110

111

end case;

end if;

112

113

end process;

114

115

116

end Behavioral;

117

118

119

```